Reducing Development Risk In Communications Applications With High-Performance Oscillators

Source: Skyworks Solutions, Inc.

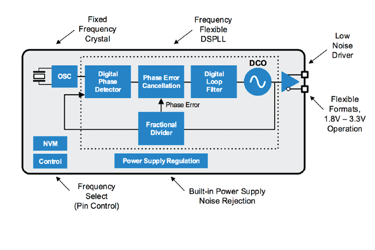

As communications and data center applications transition to higher data rates to support rapidly increasing Internet traffic demands, SerDes reference clock performance is becoming increasingly important.

If reference clock jitter is too high, it results in unacceptably high system bit-error rate (BER), lost traffic or loss of system communication. In addition, 56G PAM4 PHYs, 100G/200G/400G Ethernet, and 100G/400G OTN require a diverse mix of frequencies, further increasing timing complexity. Download the application note to learn more.

access the Application Note!

Log In

Get unlimited access to:

Trend and Thought Leadership Articles

Case Studies & White Papers

Extensive Product Database

Members-Only Premium Content

Welcome Back! Please Log In to Continue.

X

Enter your credentials below to log in. Not yet a member of RF Globalnet? Subscribe today.

Subscribe to RF Globalnet

X

Subscribe to RF Globalnet

This website uses cookies to ensure you get the best experience on our website. Learn more